Edition 1.0 2017-10

# TECHNICAL REPORT

Semiconductor devices – Scan based ageing level estimation for semiconductor devices

INTERNATIONAL ELECTROTECHNICAL COMMISSION

ICS 31.080.01 ISBN 978-2-8322-4903-1

Warning! Make sure that you obtained this publication from an authorized distributor.

# CONTENTS

| FOREW                                                                                       | /ORD                                                                    | 3  |

|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|----|

| INTRO                                                                                       | DUCTION                                                                 | 5  |

| 1 Sc                                                                                        | ope                                                                     | 6  |

|                                                                                             | rmative references                                                      |    |

|                                                                                             | rms, definitions and abbreviated terms                                  |    |

| 3.1                                                                                         | Terms and definitions                                                   |    |

| 3.2                                                                                         | Abbreviations                                                           |    |

| 4 Ag                                                                                        | eing level                                                              |    |

| 4.1                                                                                         | Overview                                                                |    |

| 4.2                                                                                         | Ageing level characterization technique (test method)                   |    |

| 4.3                                                                                         | Architecture and operation                                              |    |

| 4.4                                                                                         | Performance estimation storage element                                  | 12 |

| 4.5                                                                                         | Simulation results                                                      | 14 |

| 4.6                                                                                         | Experimental results                                                    | 14 |

| Bibliogr                                                                                    | aphy                                                                    | 17 |

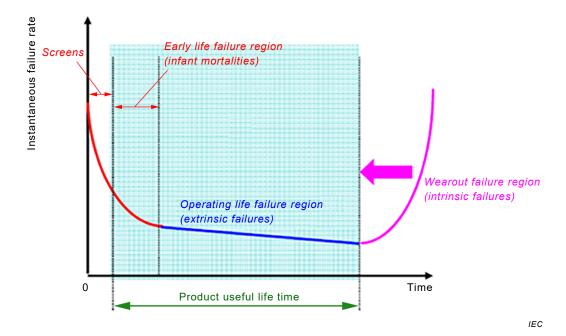

| Figure '                                                                                    | 1 – Reliability bathtub curve                                           | 5  |

| Figure 2 – Schematic of ageing level estimation technique                                   |                                                                         | 9  |

| Figure 3 – A guard band and estimated ageing level                                          |                                                                         | 10 |

| Figure 4                                                                                    | 4 – Ageing level monitoring and scan chain architecture                 | 11 |

| Figure 5 – State diagram for performance estimation controller                              |                                                                         |    |

| Figure 6 – Modified scan cell architecture                                                  |                                                                         |    |

| Figure 7 – Operations of shadow latch, storage element, and PERC according to CLK and PECLK |                                                                         |    |

|                                                                                             | 3 – Simulation results for a case in which ageing occurs on a data path |    |

| Figure 9 – PECLKs for various delay points and their results                                |                                                                         |    |

| i iguie s                                                                                   | 7 LOLING TOT VARIOUS WEIRLY POINTS AND THEIR TESUITS                    | 10 |

| Table 1 – Power consumption compared with prior work                                        |                                                                         |    |

#### INTERNATIONAL ELECTROTECHNICAL COMMISSION

#### SEMICONDUCTOR DEVICES -

### Scan based ageing level estimation for semiconductor devices

#### **FOREWORD**

- 1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports, Publicy Available Specifications (PAS) and Guides (hereafter referred to as "IEC Publication(s)"). Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and non-governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely with the International Organization for Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

- 2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested IEC National Committees.

- 3) IEC Publications have the form of recommendations for international use and are accepted by IEC National Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any misinterpretation by any end user.

- 4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications transparently to the maximum extent possible in their national and regional publications. Any divergence between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in the latter

- 5) IEC itself does not provide any attestation of conformity. Independent certification bodies provide conformity assessment services and, in some areas, access to IEC marks of conformity. IEC is not responsible for any services carried out by independent certification bodies.

- 6) All users should ensure that they have the latest edition of this publication.

- 7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and members of its technical committees and IEC National Committees for any personal injury, property damage or other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC Publications.

- 8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is indispensable for the correct application of this publication.

- 9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

The main task of IEC technical committees is to prepare International Standards. However, a technical committee may propose the publication of a technical report when it has collected data of a different kind from that which is normally published as an International Standard, for example "state of the art".

IEC TR 63133, which is a technical report, has been prepared by IEC technical committee 47: Semiconductor devices.

The text of this technical report is based on the following documents:

| Enquiry draft | Report on voting |

|---------------|------------------|

| 47/2405/DTR   | 47/2425/RVDTR    |

Full information on the voting for the approval of this technical report can be found in the report on voting indicated in the above table.

This document has been drafted in accordance with the ISO/IEC Directives, Part 2.

The committee has decided that the contents of this document will remain unchanged until the stability date indicated on the IEC website under "http://webstore.iec.ch" in the data related to the specific document. At this date, the document will be

- · reconfirmed,

- withdrawn,

- replaced by a revised edition, or

- amended.

A bilingual version of this publication may be issued at a later date.

IMPORTANT – The 'colour inside' logo on the cover page of this publication indicates that it contains colours which are considered to be useful for the correct understanding of its contents. Users should therefore print this document using a colour printer.

#### INTRODUCTION

A semiconductor device has an important role in reliability-critical applications, e.g., space, air and road vehicles, medical equipment. Although new technology has improved performance, power efficiency, cost efficiency etc., but the reliability becomes a serious threat [1]<sup>1</sup>. As can be seen in Figure 1, failure rate is decreases in early life, and low constant failure rate is preserved for a while, then wear out failure rate is increases significantly. Especially for reliability-critical applications, it is important to precisely monitor the ageing level to forewarn of any impending catastrophic failure. The semiconductor ageing is caused by negative/positive bias temperature instability, hot carrier injection, and time dependent dielectric breakdown, electro migration, and stress migration, etc. Path delay is known to be increased due to various ageing failures. Although a few ageing monitoring techniques have been developed [2 to 5], the ageing level has not been precisely diagnosed. For reliability-critical applications, the ageing level information can be utilized for taking adequate measures timely, e.g., device replacement, performance switching using dynamic voltage-frequency scaling. This document describes an efficient technique to monitor the ageing and characterize the ageing level.

Figure 1 - Reliability bathtub curve

<sup>1</sup> Numbers in square brackets refer to the Bibliography.

## **SEMICONDUCTOR DEVICES -**

# Scan based ageing level estimation for semiconductor devices

## 1 Scope

This Technical Report specifies a design technique of performance estimation storage element, which can monitor semiconductor ageing and characterize ageing level. The estimated ageing level can be used to improve the reliability of system.

#### 2 Normative references

There are no normative references in this document.